⚡ Кэш и регистры: невидимая элита

Кратко: Регистры и кэш — это сверхбыстрая память внутри процессора. Регистры — личное рабочее место процессора, где числа лежат прямо под рукой. Кэш — это умный помощник, который заранее подтаскивает данные из медленной оперативки, чтобы процессор не ждал. Вместе они творят магию скорости: регистры работают за 1 такт, кэш L1 — за 3–4 такта, а без них пришлось бы ждать ответа от RAM сотни тактов.

▫️Регистры — личный стол процессора · Как устроены: это крошечные ячейки памяти (триггеры) прямо в ядре процессора. Доступ к ним встроен в команды — не надо искать адрес, вычислять, просто взял и положил.

· Типы регистров: — Регистры общего назначения (РОН) — хранят числа и адреса. В 32-битном процессоре их 8, каждый по 32 бита. К ним можно обращаться целиком или половинками. — Регистр флагов (EFLAGS) — хранит флаги результата: Zero (ноль), Negative (отрицательно), Overflow (переполнение) и другие — Указатель команд (EIP/IP) — всегда содержит адрес следующей команды — Сегментные регистры — указывают на сегменты памяти — Регистры плавающей точки — для вещественных чисел · Скорость: 0.5–1 такт. Это абсолютный рекордсмен.

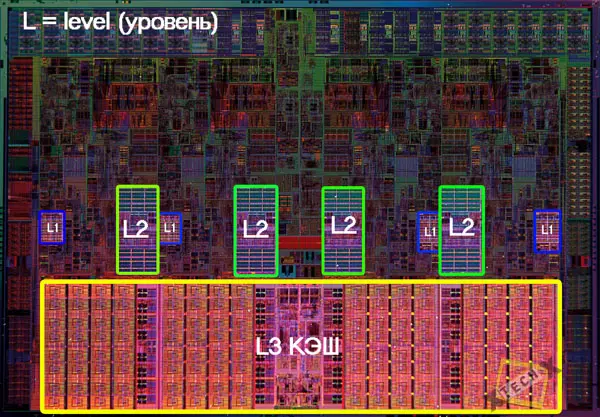

▫️Кэш — иерархия подручных складов Кэш — это буфер между процессором и медленной RAM. Данные хранятся не по байтам, а кэш-линиями — блоками по 64 байта в современных CPU. · Уровни кэша: — L1 (32–512 КБ) — самый быстрый (~1.2 нс, 3–4 такта). Часто разделён на кэш данных (L1d) и инструкций (L1i) — L2 (128 КБ – 24 МБ) — подольше (~3 нс, 10–12 тактов) — L3 (2–32 МБ) — ещё медленнее (~12 нс, 30–50 тактов), общий для всех ядер — L4 — редко, в серверах и HPC · Как работает: процессор сначала ищет данные в L1. Если мимо — идёт в L2, потом в L3, и только потом в RAM (десятки и сотни тактов). При этом из RAM подтягивается сразу целая кэш-линия (64 байта), потому что велик шанс, что соседние данные скоро понадобятся.

▫️Культурный феноме · Мем «оптимизируй под кэш» — программисты годами учатся не бегать по памяти зигзагами · RISC против CISC — у RISC много регистров и простые команды, у CISC мало регистров и сложные. RISC победил в мобильных процессорах · Локальность данных — святой грааль: храни данные рядом, обращайся последовательно

▫️Современное положение (2026) · В Ryzen Zen 4: L1 — 32КБ данных + 32КБ инструкций на ядро, L2 — 1МБ на ядро, L3 — до 32МБ общий. L2 чуть замедлился (14 тактов вместо 12), но стал больше · Кэш-линия по-прежнему 64 байта — стандарт · Процессоры учатся предсказывать, какие данные понадобятся (prefetching). В современных Intel и AMD prefetcher тянет следующие кэш-линии, пока вы читаете текущие